FPGAWorkshop17Notes

From HacDC Wiki

PicoBlaze Flow Instructions

THIS SET OF INSTRUCTIONS ASSUMES THE READER IS FAMILIAR WITH THE ISE SUITE FLOW FOR CREATING, IMPLEMENTING AND PROGRAMING PROJECTS.

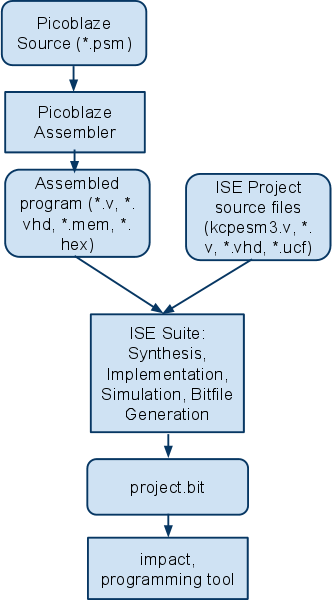

Overview of Picoblaze / ISE Development flow

The PicoBlaze development flow is different from the FPGA flow we've seen so far. We have to use a new tool, a PicoBlaze assembler, in conjunction with the ISE tool set.

I reccomend placing a folder named 'asssembly' or something else memorable in the root of your desired ISE project. This will keep an entire project togetheer in a single directory. You'll want to copy the ROM_form.vhd file from the picoblaze processor distribution to a convenient place, such as ./assembly directory or your project directory. We'll need to have a copy of this to use later.

The new tool we'll be working with today is openpicide. It is a project management IDE, Syntax check, program assembler and device simulator. It is opensource project, based on the QT framework. We'll be using it to generate the program ROM as a VHDL block ram file, which will be used with our design. The structure of our example project will look like the following:

- top_level.v

- embedded_kcpsm3.v

- kcpsm3.v

- prog_rom.vhd - This is the file generated by the assembler.

- embedded_kcpsm3.v

- project_constraints.ucf

In general, a picoblaze design would look like this

- top_level.v

- embedded_kcpsm3.v

- kcpsm3.v

- prog_rom.vhd - This is the file generated by the assembler.

- kcpsm3.v

- periperal1.v

- periperal2.v

- sub_module1.v

- ....

- other logic as needed

- embedded_kcpsm3.v

- project_constraints.ucf

Picoblaze simple example / toolchain tutorial

To begin, make sure you've got Xilinx ISE and OpenpicIDE installed. You can obtain openpicIDE here http://openpicide.org/ You'll also need to get the picoblaze download package.

First, we'll create the ISE project. Create a new project called picoblaze_example1 in your projects directory. Add copies of the following files from the picoblaze download package.

- embedded_kcpsm3.v

- kcpsm3.v

Then create 2 new source files

- constraints.ucf

- picoblaze_example1.v.

Copy and paste the contents of these files from the wiki [see below]. You should note that your missing a file, prog_rom, which is in the embedded_kcpsm3 module. Do not attempt to implement the design - it will not work until we generate the program ROM.

When openpicide opens, you'll want to create a project. You should save the project file in your 'assembly' folder. Under the settings for the project, you'll need to do the following:

- Set the processor to Xilinx picoblaze

- Set the VHDL template name to "prog_rom"

- Set the vhdl source file to the ROM_form.vhd file we copied earlier.

- You can leave the rest of the settings to their default values.

You'll then need to create a new file - use the new file button in the upper left corner. Copy and paste the 1st example source file from the wiki. Run a syntax check on the code to make sure it is correct, and then generate a VHDL memory file from the code. Save the file as "prog_rom_example1.vhd" in your assembly section. You can now move back to ISE.

Now, add the program file "prog_rom_example1.vhd" to your project, using "Add Copy of Source". You'll notice that the prog_rom module is no longer missing, and you can now implement the design. After programming the board, you should now see the LED's flipping on and off; if so, you have a working Picoblaze toolchain.

constraints.ucf

# # UCF For Picoblaze Examples # # Period constraint for 50MHz operation # NET "CLK_50MHZ" PERIOD = 20.0ns HIGH 40%; # # soldered 50MHz Clock. # NET "CLK_50MHZ" LOC = "C9" | IOSTANDARD = LVTTL; # Simple LEDs # Require only 3.5mA. # NET "LED<0>" LOC = "F12" | IOSTANDARD = LVTTL | SLEW = SLOW | DRIVE = 4; NET "LED<1>" LOC = "E12" | IOSTANDARD = LVTTL | SLEW = SLOW | DRIVE = 4; NET "LED<2>" LOC = "E11" | IOSTANDARD = LVTTL | SLEW = SLOW | DRIVE = 4; NET "LED<3>" LOC = "F11" | IOSTANDARD = LVTTL | SLEW = SLOW | DRIVE = 4; NET "led<4>" LOC = "C11" | IOSTANDARD = LVTTL | SLEW = SLOW | DRIVE = 4; NET "led<5>" LOC = "D11" | IOSTANDARD = LVTTL | SLEW = SLOW | DRIVE = 4; NET "led<6>" LOC = "E9" | IOSTANDARD = LVTTL | SLEW = SLOW | DRIVE = 4; NET "led<7>" LOC = "F9" | IOSTANDARD = LVTTL | SLEW = SLOW | DRIVE = 4; # Simple switches # Pull UP resistors used to stop floating condition during switching. # sw0 NET "FPGA_RESET" LOC = "L13" | IOSTANDARD = LVTTL | PULLUP; # sw1 NET "SW1" LOC = L14 | | IOSTANDARD = LVTTL | PULLUP;

picoblaze_example1.v

module picoblaze_example1(

input FPGA_RESET,

input CLK_50MHZ,

output [7:0] LED

);

wire clock = CLK_50MHZ;

// reset is active high.

// if no reset signal input

// then tie reset to zero here.

wire reset = FPGA_RESET;

wire [7:0] port_id;

wire write_strobe;

wire read_strobe;

wire [7:0] out_port;

wire [7:0] in_port=0;

wire interrupt=0;

wire interrupt_ack;

embedded_kcpsm3 EMBEDDED(

.port_id(port_id),

.write_strobe(write_strobe),

.read_strobe(read_strobe),

.out_port(out_port),

.in_port(in_port),

.interrupt(interrupt),

.interrupt_ack(interrupt_ack),

.reset(reset),

.clk(clock)

);

// only one bit written to by picoblaze, the LED.

// therefore don't need to decode port_id.

// if write_strobe asserts, grab out_port[0] and

// hold it in userbit.

reg [7:0] userbit = 0;

always @(posedge clock) begin

if(write_strobe) begin

userbit <= out_port;

end

end

assign LED = userbit;

endmodule