## FPGA Workshop

Introduction to Sequential Circuits

HacDC Nov 2009.

## Why Sequential?

- It helps when the regulator is in town

- Time can be used to regulate operations

- I will be ready by tomorrow/one hour/(1/1Mhz)

- So far, we have implemented circuits that are asynchronous (meaning do not use a clock to regulate when the output becomes ready)

- This may be useful when you just have one function to implement, but is problematic if you need to implement functions in series.

# Introducing the Clock

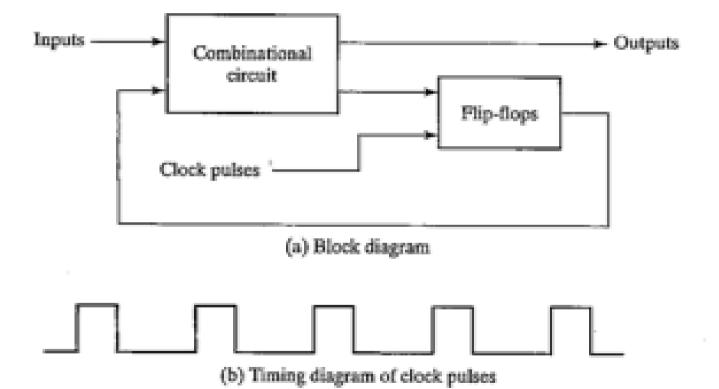

- Combinatorial vs

Sequential logic

- A defining feature of Sequential logic is the presence of a clock and a memory element

- Not only does the output depend on where we are in (clock) time, but also what were the previous outputs (memory)

- Will be used to create Finite State Machines

- "Where am I? What has changed? Where should I go?"

### Latch vs Flip Flop

- Often (historically) has been used interchangeably

- In this class, we will define a distinction between the two, for logical reasons

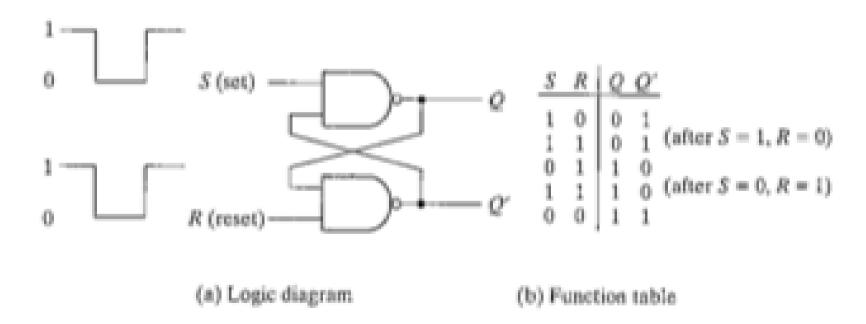

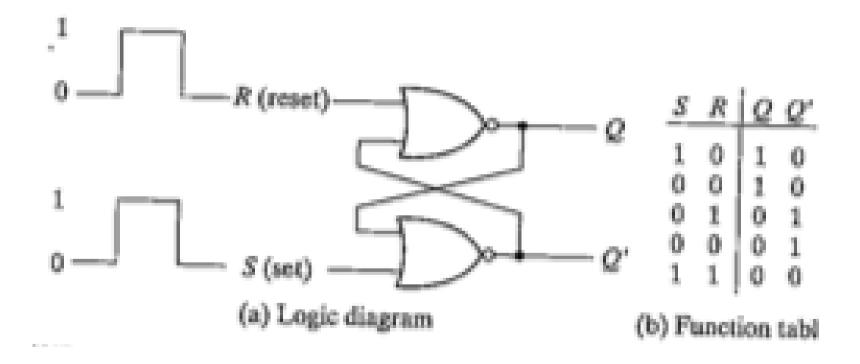

- All Latches/Flip Flops are defined by a function table

- Latch is a non-clocked memory

- Flip Flop is a Latch with a clock input

#### Latches – SR Latch

- Set or Reset?

- Bistate vibrator!!

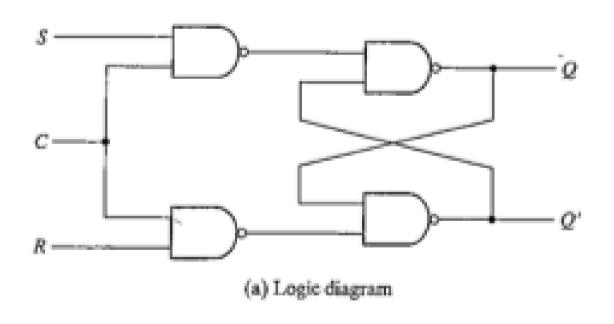

#### Latches - SR Latch

Implemented with NOR Gates

#### Latches - SR Latch

Implemented with an additional control input

| C S R                            | Next state of Q                                                       |

|----------------------------------|-----------------------------------------------------------------------|

| 0 X X<br>1 0 0<br>1 0 1<br>1 1 0 | No change No change Q = 0; Reset state Q = 1; set state Indeterminate |

(b) Function table

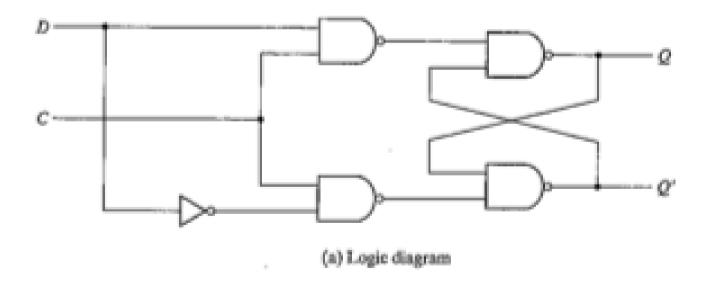

#### Latches – D Latch

- Simply follows the input

- An SR Latch with no ambiguous states

| C D Ne | xt state of Q                                |

|--------|----------------------------------------------|

| 10 0   | change<br>= 0; Reset state<br>= 1; Set state |

(b) Function table

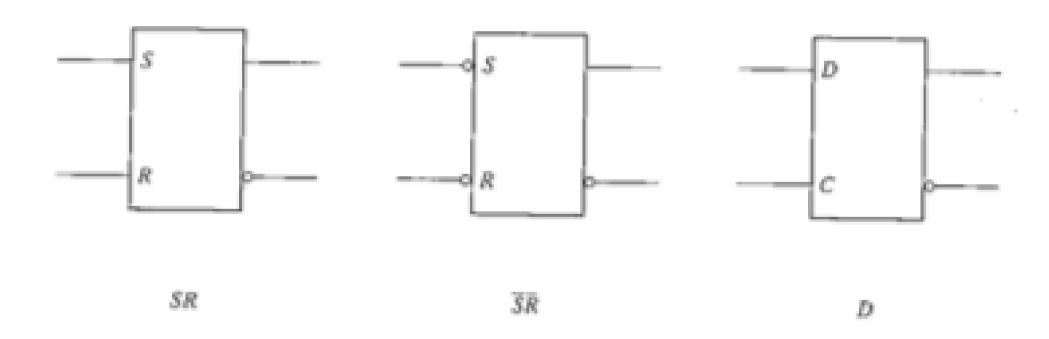

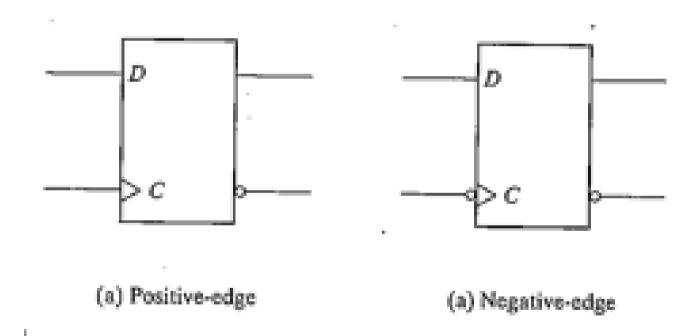

# Latches - Symbols

Circle means invert!

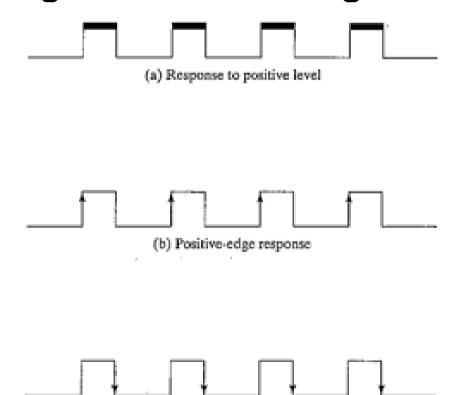

#### What to do with the Clock?

- Its useful to define a time period in which the output will be ready (e.g. high time, or low time)

- Even better, get locked to edge of the clock!

(c) Negative-edge response

## Introducing the Flip Flop!

- Add a clock, and you have a Flip-Flop

- Output change in response to inputs and the clock!

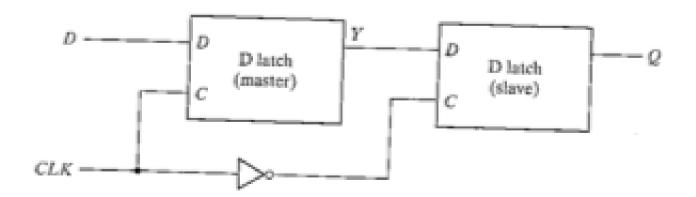

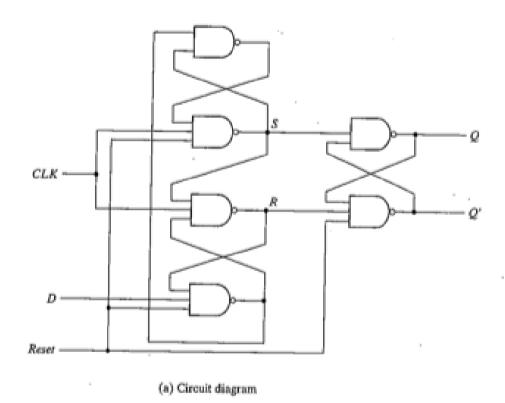

- One way to implement an edge triggered Flip Flop is using a Master/Slave Implementation

## Flip Flops – D

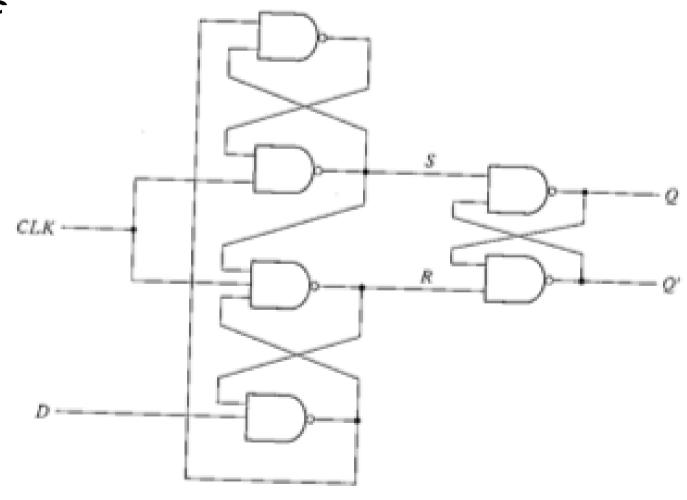

Positive Edge Triggered Flip Flop using three SR Latches

# Where to trigger?

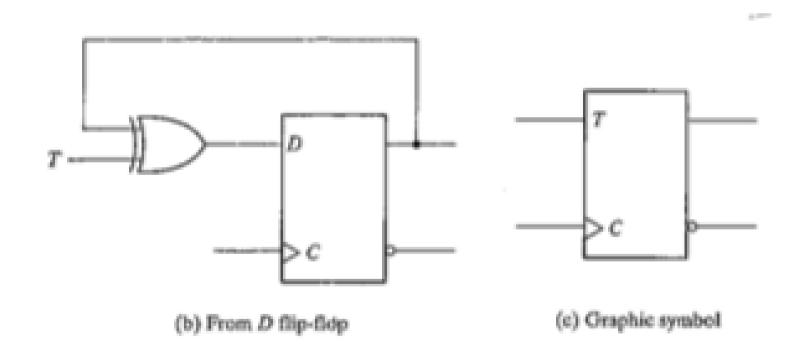

# Flip Flops - T

Boring! but sometimes useful

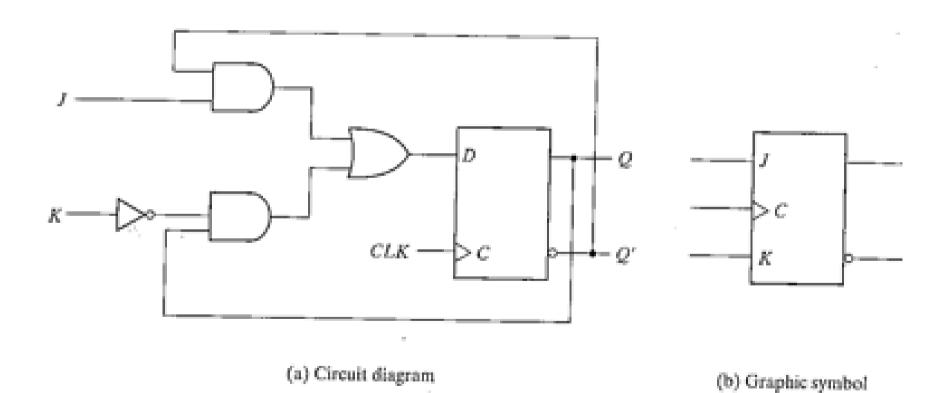

## Flip Flops - JK

- Badass flip-flop

- Allows you to set/reset or complement the previous input

Table 5-1 Flip-Flop Characteristic Tables

| JK Flip-Flop             |                         |                                         |  |  |

|--------------------------|-------------------------|-----------------------------------------|--|--|

| J K                      | Q(t + 1)                |                                         |  |  |

| 0 0<br>0 1<br>1 0<br>1 1 | Q(t)<br>0<br>1<br>Q'(t) | No change<br>Reset<br>Set<br>Complement |  |  |

No change Complement

| D Flip-Flop |       | T Flip-Flop  |   |               |

|-------------|-------|--------------|---|---------------|

| D           | Q(t + | 1)           | T | Q(t+1)        |

| 0           | 0     | Reset<br>Set | 0 | Q(t)<br>Q'(t) |

# Flip Flops - JK

What if I want a flip flop with a hammer?

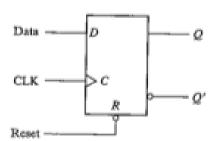

# Asynchronous Reset

(b) Graphic symbol

| R | C | D | Q | Q' |

|---|---|---|---|----|

| 0 | х | х | 0 | 1  |

| 1 | Ť | 0 | 0 | 1  |

| 1 | † | 1 | 1 | 0  |

(b) Function table

Fine.

### **Problems**

•

- None.